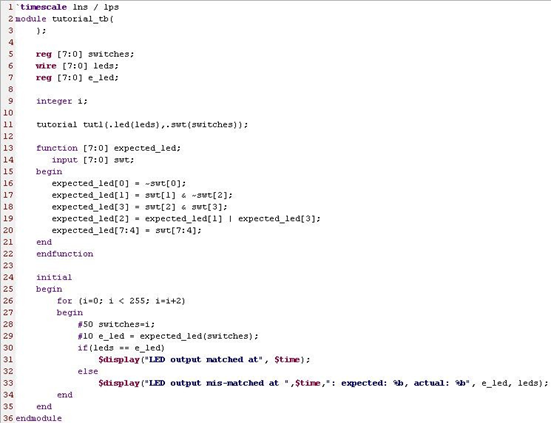

3. 使用Testbench的一个例子 第 1 行定义了`timescale 指令。 第 2 行和第 3 行定义了测试平台模块名称。请注意,通常, testbench 模块的端口列表中不列出端口。 第 5 行将拨动开关定义为 reg 数据类型,因为它将用于提供激励。它连接到被测试(tutorial)的实例化设备。 第 11 行使用实例名称 tut1 和输入/输出端口实例化测试(tutorial)中的设计。 第 13 行到第 22 行定义了计算预期输出的function。 第 24 至 35 行使用 initial 过程描述来定义激励。可以在仿真器控制台窗口中使用 system task $ display 来查看第 31 行和第 33 行生成的消息。 第 29 行通过传递开关参数调用函数 expected_led,并将返回的(计算过的)输出分配给 e_led。 e_led 在第 7 行定义为 reg 类型,因为它在过程语句(初始)中接收函数调用的输出。 第 28 和 29 行还分别定义惯性延迟 50 和 10,以模拟延迟

|