日志

上拉电阻取值问题

|

漏极开路上拉电阻取值为何不能很大或很小?

如果上拉电阻值过小,Vcc灌入端口的电流(Ic)将较大,这样会导致MOS管V2(三极管)不完全导通(Ib*β<ic),有饱和状态变成放大状态,这样端口输出的低电平值增大(i2c协议规定,端口输出低电平的最高允许值为0.4v)

</ic),有饱和状态变成放大状态,这样端口输出的低电平值增大(i2c协议规定,端口输出低电平的最高允许值为0.4v)<>

如果上拉电阻过大,加上线上的总线电容,由于RC影响,会带来上升时间的增大(下降延是芯片内的晶体管,是有源驱动,速度较快;上升延是无源的外接电阻,速度慢),而且上拉电阻过大,即引起输出阻抗的增大,当输出阻抗和负载的阻抗可以比拟的时,则输出的高电平会分压而减少。

I2C的上拉电阻可以是1.5K,2.2K,4.7K, 电阻的大小对时序有一定影响,对信号的上升时间和下降时间也有影响,一般接1.5K或2.2K

(实验:接入200K上拉电阻,结果观察到信号上升时间增大,方波变成三角波)

I2C上拉电阻确定有一个计算公式:

Rmin={Vdd(min)-o.4V}/3mA

Rmax=(T/0.874) *c, T=1us 100KHz, T=0.3us 400KHz

C是Bus capacitance

Rp最大值由总线最大容限(Cbmax)决定,Rp最小值由Vio与上拉驱动电流(最大取3mA)决定;

于是 Rpmin=5V/3mA≈1.7K(@Vio=5V)或者2.8V/3mA≈1K(@Vio=2.8V)

Rpmax的取值:参考周公的I2C总线规范中文版P33图39与P35图44

标准模式,100Kbps总线的负载最大容限<=400pF;快速模式,400Kbps总线的负载最大容限<=200pF,根据具体使用情况、目前的器件制造工艺、PCB的走线距离等因素以及标准的向下兼容性,设计中以快速模式为基础,即总线负载电容<200pF,也就是传输速度可以上到400Kbps是不成问题的。于是Rpmax可以取的范围是1.8K~7K

@ Vio=5V对应50pF~200pF

根据Rpmin与Rpmax的限制范围,一般取5.1K @ Vio=5V ,

负载容限的环境要求也容易达到。在2.8V系统中,console设计选3.3K,portable/handset等低供耗的设计选4.7K牺牲速度换取电池使用时间

总的来说:电源电压限制了上拉电阻的最小值 ; 负载电容(总线电容)限制了上拉电阻的最大值

补充:在I2c总线可以串连300欧姆电阻RS可以用于防止SDA和SCL线的高电压毛刺

: I2c从设备的数量受总线电容,<=400pF的限制

上拉电阻阻值的确定

由于I2C接口采用Open

Drain机制,器件本身只能输出低电平,无法主动输出高电平,只能通过外部上拉电阻RP将信号线拉至高电平。因此I2C总线上的上拉电阻是必须的!

RP不宜过小,一般不低于1KΩ

一般IO

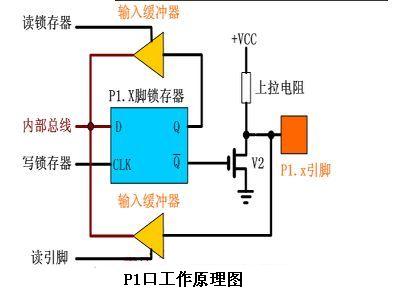

端口的驱动能力在2mA~4mA量级。如果RP阻值过小,VDD灌入端口的电流将较大,这样会导致MOS管不完全导通,有饱和状态变成放大状态,这样端口输出的低电平值增大(I2C协议规定,端口输出低电平的最高允许值为0.4V);如果灌入端口的电流过大,还可能损坏端口。故通常上拉电阻应选取不低于1KΩ的电阻(当VDD=3V时,灌入电流不超过3mA)。

RP不宜过大,一般不高于10KΩ

由于端口输出高电平是通过RP实现的,线上电平从低到高变化时,电源通过RP对线上负载电容CL充电,这需要一定的时间,即上升时间。端口信号的上升时间可近似用充电时间常数RPCL乘积表示。

信号线负载电容(对地)由多方面组成,包括器件引脚、PCB信号线、连接器等。如果信号线上挂有多个器件,负载电容也会增大。比如总线规定,对于的400kbps速率应用,信号上升时间应小于300ns;假设线上CL为20PF,可计算出对应的RP值为15KΩ。

如果RC充电时间常数过大,将使得信号上升沿变化缓慢,达不到数据传输的要求。

因此一般应用中选取的都是几KΩ量级的上拉电阻,比如都选取4K7的电阻。

小阻值的RP电阻增大了端口Sink电流,故在可能的情况下,RP取值应稍大一点,以减少耗电。另外,通产情况下,SDA,SCL两条线上的上拉电阻取值是一致的,并上拉到同一电源上。

PCB布局布线与抗干扰设计

I2C信号线属于低速控制线,在手机PCB设计时,按通常的控制IO对待即可,无需做特别的保护设计,一般不用担心受到噪声源干扰。

但在一些特定的情况下,比如折叠、滑盖机型中,I2C的两根信号线需要通过转轴或滑轨处的FPC,此时由于信号路径比较长,距离天线比较近,而且Open

drain的输出级对地阻抗大,对干扰比较敏感,因此比较容易受到RF信号源的干扰。在这种情况下,就应适当注意对I2C信号线的保护。比如I2C两条信号线(SDA,SCL)等长度地平行走线,两边加地线进行保护,避免临近层出现高速信号线等。

上拉电阻应安置在OD输出端附近。当I2C总线上主从器件(Master &

Slave)两端均为OD输出时,电阻放置在信号路径的中间位置。当主设备端是软件模拟时序,而从设备是OD输出时,应将电阻安置在靠近从设备的位置。

I2C协议还定义了串联在SDA、SCL线上电阻Rs。该电阻的作用是,有效抑制总线上的干扰脉冲进入从设备,提高可靠性。这个电阻的选择一般在100~200ohm左右。当然,这个电阻并不是必须的,在恶劣噪声环境中,可以选用。

比如常用的FM

接收模块或者Capsense触摸感应功能块,都是通过I2C接口控制的。I2C接口信号从处理器出发,经过PCB上的信号路径,进入上述电路单元。I2C信号线上载有一定干扰,这种干扰虽然幅度并不很大,但还是会影响敏感的FM接收模块或Capsense触摸感应功能块。此时,可以通过在靠近FM模块或触摸感应模块的I2C信号线上串接Rs电阻,即可有效降低干扰的影响。此外,上拉电阻端的电源也要进行退耦处理。

软件模拟I2C时序

由于一般的I2C应用速率并不高(400kbps),使用处理器的IO口模拟I2C波形,完全可以胜任(处理器一般担任Master,占有I2C通信的控制权,无需担心随机的I2C通信服务中断其他任务的执行)。

处理器分配给I2C任务的IO口,要求可以输出高低电平,还能配置为输入端口。处理器根据总线规范以及从设备的时序要求,利用2条IO信号线,模拟I2C接口时序波形,进行I2C通信。

处理器发送数据时,通过IO口输出高电平,上升时间基本与外部上来电阻阻值无关,且比用外部上拉电阻上拉到高电平快很多。处理器在接受数据时,即便上拉电阻阻值选的大一些,从设备输出数据的波形上升沿缓慢,但由于处理器使用软件采样的而非硬件采样,因此,对数据传输的结果并不影响。也就是说,使用IO口模拟I2C时序时,上拉电阻阻值可以适当选的大一些。

需要指出的是,使用软件模拟最多只能完成单Master的应用,对于多Master应用,由于需要进行总线控制权的仲裁管理,使用软件模拟的方法很难完成。

I2C总线空闲的时候,两条信号线应该维持高电平。否则,上拉电阻上会有耗电。特别是在上电过程中,IO线上电平也应保持在高电平状态。也就是说:当Master的I2C使用的是IO软件模拟时,一定要保证该两个IO上电默认均为输入(或高阻)或者输出高电平,切不可默认为输出低电平。IO默认为输入时,可以通过外部上拉电阻将I2C信号线拉至高电平。

I2C应用中上拉电阻电源问题

在部中分应用中,还存在主从设备以及上拉电阻电源不一致的情况,比如Camera模组。在很多设计方案中,Camera模组不工作时,并不是进入Power

Down模式,而是直接关闭模组供电VDDS。此时,处理器与模组相互连接的所有信号线都应该进入高阻态,否则就会有电流漏入模组;而对于此时的I2C控制信号线来说,由于上拉电阻的存在,必须关断上拉电阻电源VDDP。如果上拉电阻使用的是系统电源VDDM(VDDP=VDDM),无法关闭,就会有漏电流进入模组;因此这种情况下,应该使用VDDS作为上拉电阻电源(VDDP=VDDS),这样上拉电阻电源与Slave电源即可同时关闭,切断了漏电路径。

另外需要注意的是,在上述应用实例中选择的IO,应该选取上电默认为输入(或高阻)才行。