|

一、CPU如何执行指令? CPU包括控制器和数据通路,数据通路从字面意思理解,就是指处理器中数据流通的路径。不同类型的指令的数据通路不一样,具体由控制器产生的控制信号决定。

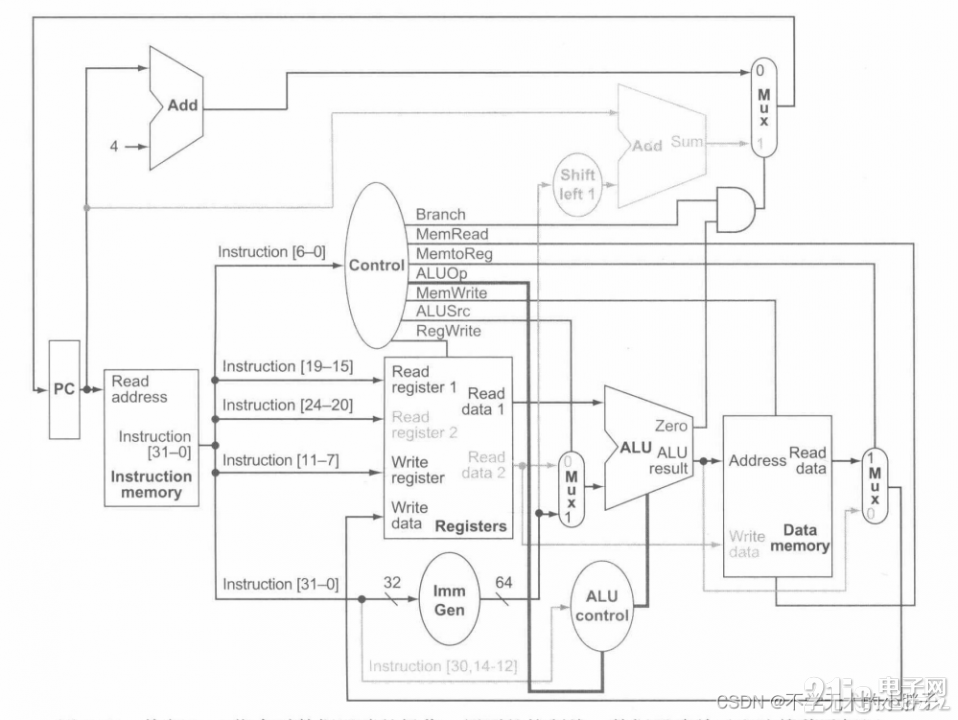

下面以一个简单的数据通路为例,介绍以下处理器执行指令的过程。

1.CPU执行指令的过程如下: (1)pc做为地址,输入到指令存储器,读取一条指令出来。这条指令是一个32bit的二进制数,里面包含了将要执行的指令的所有信息,包括指令类型(opcode),指令执行的功能(func3,func7),立即数部分(imme),源寄存器(rs1,rs2),目的寄存器(rd)。

(2)将读出来的指令进行译码,输入到不同的部件。比如,rs1,rs2,rd输入到寄存器堆,将立即数部分进行立即数扩展,将opcode输入到控制部件,产生控制信号。将func3,func7输入到子控制模块,产生ALU的控制信号。 (3)译码出来的寄存器号,输入到寄存器堆,读出寄存器号对应的数据Read_data1和Read_data2。 对于R-type指令,进行的操作就是两个寄存器的数据进行运算。 对于I-type指令,进行的操作是一个寄存器的数据与立即数进行运算。 因此这里要产生立即数,并且需要一个二选一选择器进行数据的选择。 (4)ALU即是运算单元,对输入的两个数据进行运算操作并且将运算结果输出,具体进行什么运算,由ALU_control产生的控制信号决定。 (5)将计算结果写回寄存器,写入到目标寄存器号对应的寄存器中。 (6)对于访存指令,如lb,lh,lw,sb,sh,sw,指令,还需要与数据存储器进行数据交换。 对于load指令,执行的操作是将数据从数据存储器的某个地址读出数据并讲这个数据写回到寄存器。 对于store指令,执行的操作是将寄存器的数据写入到数据存储器的某个地址内。 这个数据存储器的地址怎么产生呢? 地址以基地址加偏移的形式给出,基地址从寄存器中取得,偏移量从立即数中得到,因此ALU进行加法运算的结果便是数据存储器的地址。 因此ALU的运算结果有两个去向,一是写回寄存器,二是作为数据存储器的地址。 (7)对于load指令,是将数据存储器的数据写回到寄存器。 因此寄存器的数据来源有两个,一是ALU的运算结果,二是从数据存储器读出的数据。 (8)对于不进行跳转的指令,每个周期pc+4,指令按顺序执行,因此需要一个加法器。为什么是加4呢? 一条指令有32bit,CPU的内存空间按字节编址,所以一条指令4个字节实际上占了4个地址空间。 (9)对于条件跳转指令,如BEQ,BNE等,满足跳转的条件时,跳转的新地址由pc加左移一位的立即数产生,又需要一个加法器。因此,pc的来源有两个,一是顺序执行,pc+4,二是条件跳转,pc+(imme2)。 (10)对于无条件跳转指令,如jal,pc+4写回寄存器,将pc+(imme2)作为新地址。对于jalr,将pc+4写回寄存器,将源寄存器的数据与立即数相加并将最低位置0,作为下一个pc。 因此,写入寄存器的数据来源变成3个:ALU的运算结果,数据存储器读出的数据,pc+4。 pc的来源也变成3个:pc+4,pc+imme,Read_data1+imme。 (11)再考虑U-type,即lui,auipc。对于lui,将立即数进行处理,写入寄存器。对于auipc,将pc+imme写入寄存器。 因此,写入寄存器的数据来源变成5个,分别是:ALU的运算结果,数据存储器读出的数据,pc+4,lui的立即数 ,auipc的pc+imme。 上图所示的数据通路并不完整,如果想实现我们提到的37条指令,必须逐条分析指令,在上图的基础上添加相应的部件。 ———————————————— 版权声明:本文为CSDN博主「不学无术的小胖子.」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。 原文链接:https://blog.csdn.net/qq_45677520/article/details/122386632

|