本帖最后由 LINGXUEG 于 2025-6-30 08:33 编辑

测量FPGA中组合逻辑电路propagation delay,理论上约80ps;

信号由脉冲发生器通过FPGA的某一个IO进去,经过可控延迟(步进约80ps),从另一个IO口出来;

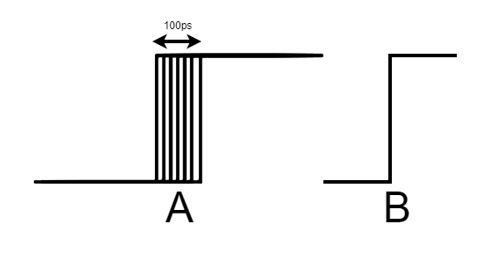

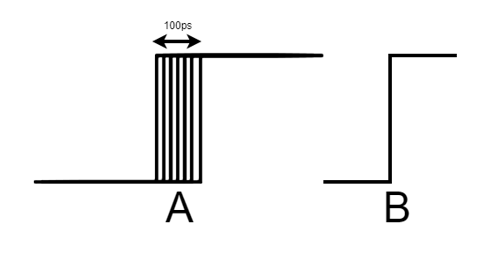

示波器设定通道B边沿触发,则脉冲发生器的抖动(jitter,最大约100ps),在B通道上表现不出来,在A通道上能看到。但实际上A通道上的抖动在B通道上也有。

问题是:如何通过测量技巧,消除抖动对测量的影响,类似共模抖动消除? 使得能够测量A相对于B的绝对延迟(ps级别) |

3434666f1860bd88cd.png (13.42 KB )

[url=] [/url] [/url]

4710866f1860db2dc6.png (13.42 KB )

[url=] [/url] [/url]

9912566f18619d62b1.png (13.42 KB )

[url=] [/url] [/url]

|