本帖最后由 dukedz 于 2025-5-6 21:24 编辑

为了测试固定相位的采样点(命令模式),我用 fpga 返回不同延迟的数据,发现即便建立时间和保持时间都足够(对于 sck 上升沿,建立时间 和 保持时间 几乎相等),qspi 控制器依然采到不稳定的错误数据

此时,延迟为负值,数据稍微提前 sck 的下降沿生效,感觉 qspi 依然处于自动调整相位的模式,否则数据不应该读错,测试时 sck 频率为 27MHz

还是说,固定相位采样点其实是在 sck 下降沿?

如果使用自动调整相位模式,同时接多路 qspi 从机,每个从机延迟不同,那么 qspi 如何确保读取不错?

即便是一个从机,首次通讯时,是如何确保数据不错?它怎么知道从机返回数据的延迟?自动调整相位的细节是怎样的?

如果主机切换为输入时,sdio 弱拉到 1/2 vcc,那么主机可以通过监控从机输出高或低电平的时间来测量延迟,但是 qspi 控制器默认应该是上拉 sdio 到 vcc,如果数据开头是 1,那么应该监控不了

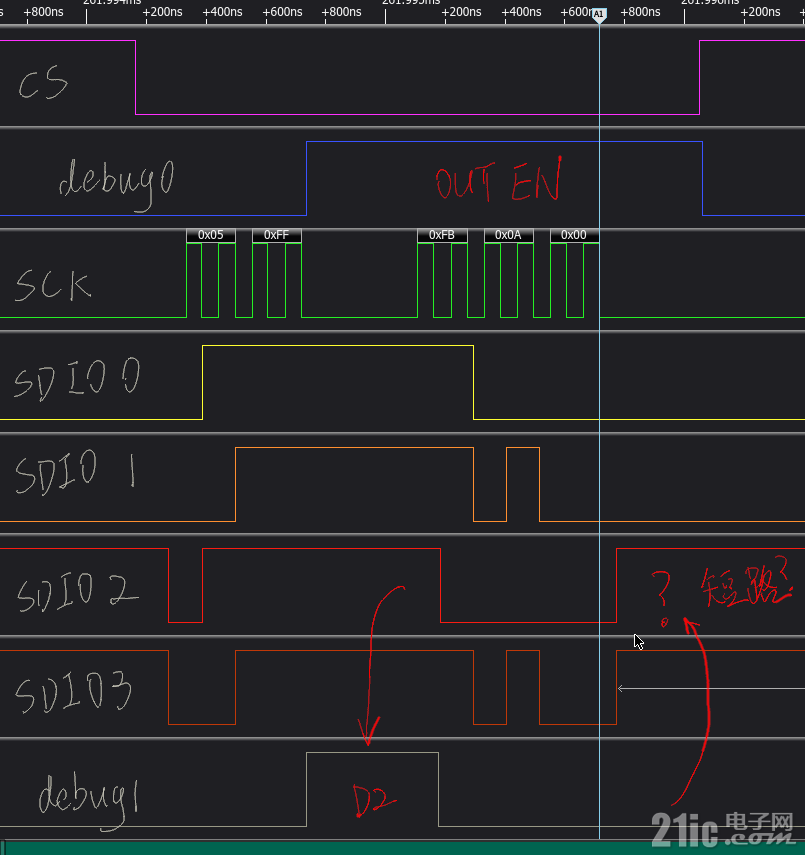

另外,发现 qspi 控制器在读数据末尾的时候,会强拉高 sdio 部分数据线,譬如这个图,我把 fpga 内部 sdio 的输出使能脚,和 sdio2 的原始数据通过其它 io 输出,发现 sdio2 在结尾处应该保持为低电平,但主机端测量 sdio2 被拉高,主从之间串了 200R 防短路电阻。这是正常的吗?主机端此时上拉强度是多少?

|

|