旁路电容作为 C 型滤波器(去耦电容)的应用领域较广, C 型滤波器随着电容的阻抗的减小,插入损耗 IL 就会增加。电容阻抗与频率成反比成为低通滤波器,理想情况下,频率越高插入损耗越大。

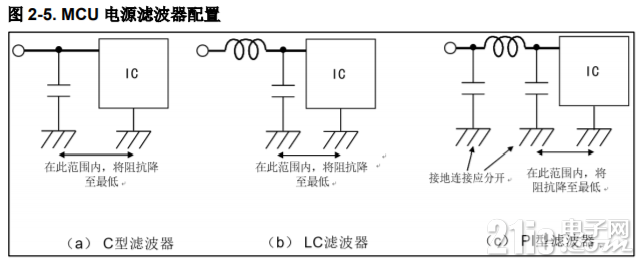

除了 C 型还有 LC 型以及 PI 型滤波器,在 C 型滤波器基础上再在 MCU 远端电源线上串一个电感/磁珠就成为 LC 滤波器,在 LC 滤波器基础上再远端在并一个电容就是 PI 型滤波。如图 2-5. MCU 电源滤波器配置

当电容器和电感器结合,如图 2-5 MCU 电源滤波器配置(b)和(c)所示,与只使用电容器相比,插入损耗特性曲线斜度会更陡。

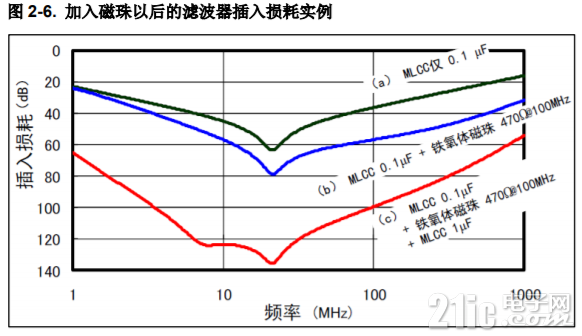

因为在衰减区,插入损耗会同时增加,当噪声需要大大削弱时,这种方法更为有用。

如图 2-6. 加入磁珠以后的滤波器插入损耗实例显示当加入电感器后,插入损耗的变化实例。

由于 MCU 的 GND 引脚与最近的电容 GND 成为噪声返回路径,所以尽量缩短两者距离来降低阻抗,当 CLC-PI 型滤波器 layout 时,两侧电容最好走之字使电容 GND 通过 VIA 分开。因为 PI 型和 LC 滤波对于干扰噪声具有较大的插入损耗,所以在抗干扰 EMS 防护MCU 时,组合去耦电路的应对强干扰的效果更好。

|