在 ADC 输入内阻不配情况下提高 ADC 准确度方法

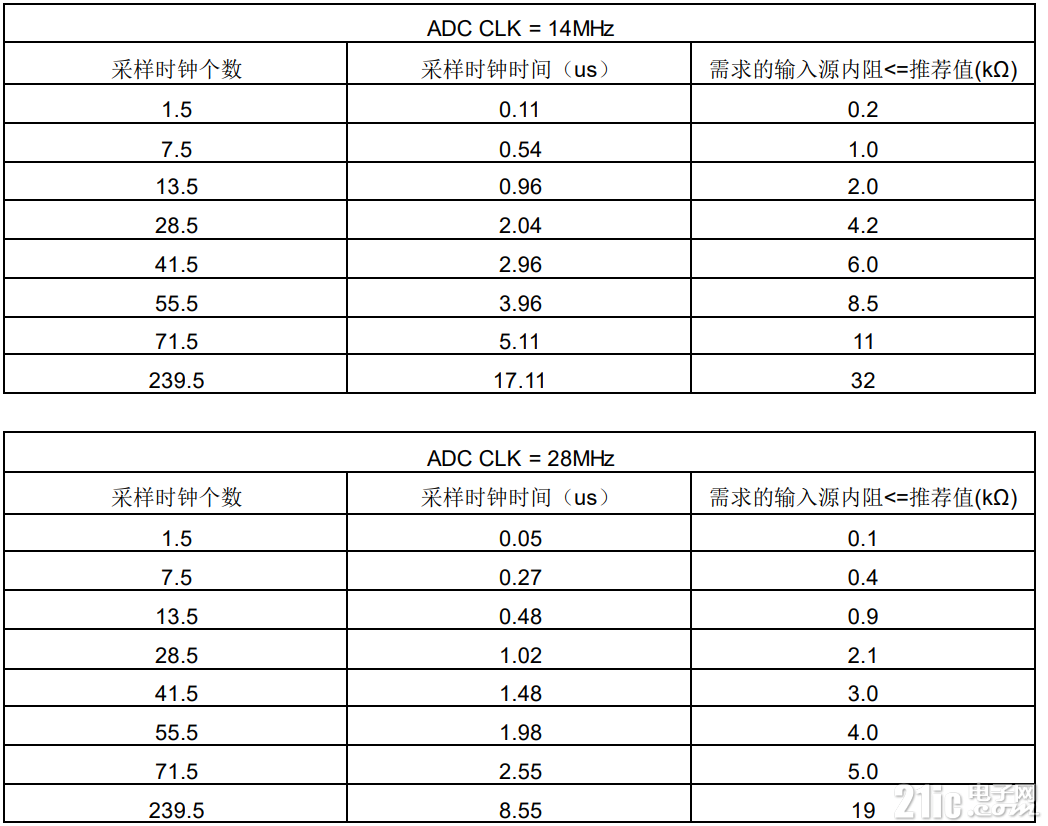

在客户应用中输入源输入电阻同推荐的值不配匹,如果输入源内阻过大,会导致 ADC 转换精度降低。以AT32F403 为例,ADC 推荐的输入源内阻如下:

为了提高 ADC 转换精度建议如下处理:

1. 可以加大采样时间来消除 ADC 采样时间不足导致的转换精度不佳;如果现在是使用 1.5 的 CLK 采样时间,发现转换精度不佳,可以用在项目允许的条件下,先按:7.5-13.5-28.5-41.5-55.5 CLK 的方式一步一步增大,直到满足要求

2. 在输入 ADC 的 I/O 口处并接电容 330pF-0.1uF,以对信号预采样

3. 若采样信号低于 |