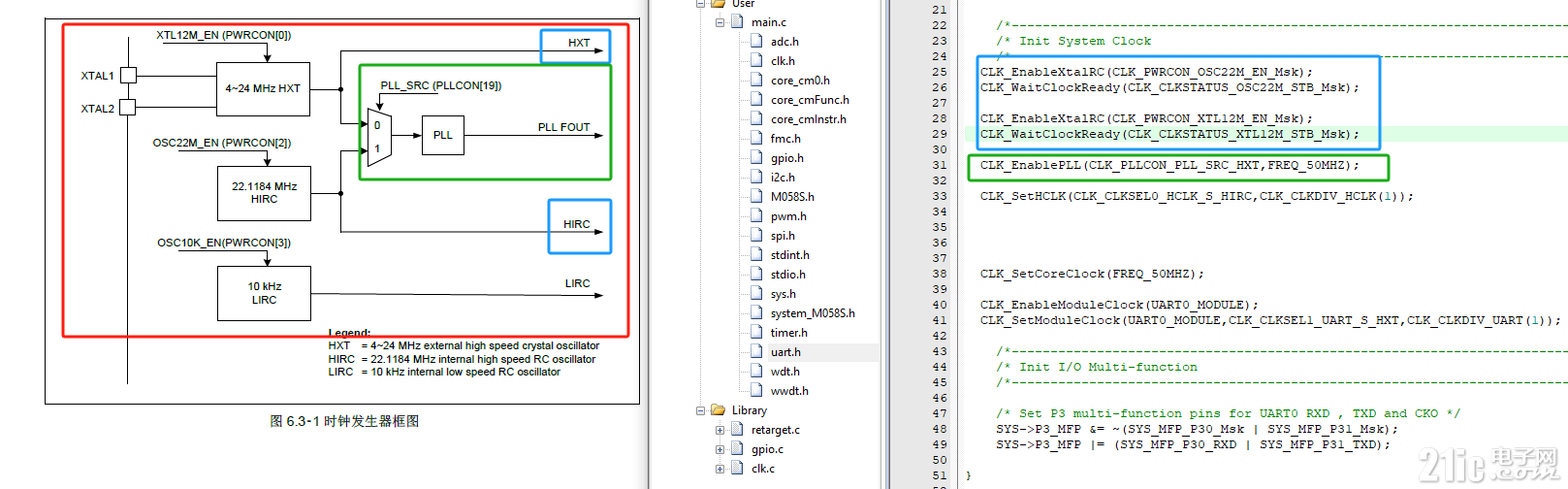

根据手册的时钟顺序,应该是先配置时钟源,是选择内部RC还是选择外部晶振,或者都配置上。

另外就是PLL,使能了PLL的同时要选择PLL从谁那获取PLL的时钟源。

上面对应的就是使能相关的时钟源。

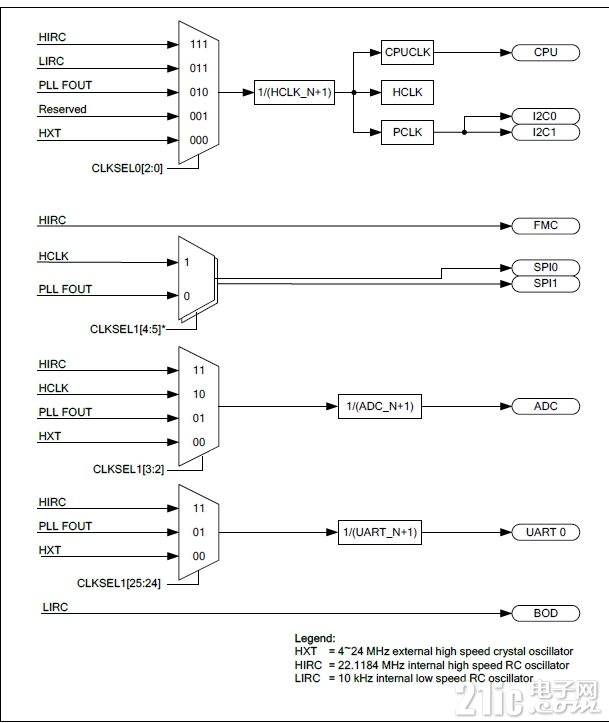

然后就是这个,注意到有个HCLK,CPUCLK,PCLK,这三个都是从同一个地方分出来,其实是同一个时钟到了三个不同的目的地。

其实他们是同一个时钟信号。所以库函数中定义获取这三个时钟的是同一个操作

- uint32_t CLK_GetHCLKFreq(void)

- {

- SystemCoreClockUpdate();

- return SystemCoreClock;

- }

- /**

- * [url=home.php?mod=space&uid=247401]@brief[/url] Get PCLK frequency

- * @param None

- * [url=home.php?mod=space&uid=266161]@return[/url] PCLK frequency

- * [url=home.php?mod=space&uid=1543424]@Details[/url] This function get PCLK frequency. The frequency unit is Hz.

- */

- uint32_t CLK_GetPCLKFreq(void)

- {

- SystemCoreClockUpdate();

- return SystemCoreClock;

- }

- /**

- * @brief Get CPU frequency

- * @param None

- * @return CPU frequency

- * @details This function get CPU frequency. The frequency unit is Hz.

- */

- uint32_t CLK_GetCPUFreq(void)

- {

- SystemCoreClockUpdate();

- return SystemCoreClock;

- }

- CLK_SetHCLK(CLK_CLKSEL0_HCLK_S_HIRC,CLK_CLKDIV_HCLK(1));

比如串口0,串口0有三个可选的时钟源,HIRC,HXT,PLL

- CLK_EnableModuleClock(UART0_MODULE);

- CLK_SetModuleClock(UART0_MODULE,CLK_CLKSEL1_UART_S_HXT,CLK_CLKDIV_UART(1));

|