|

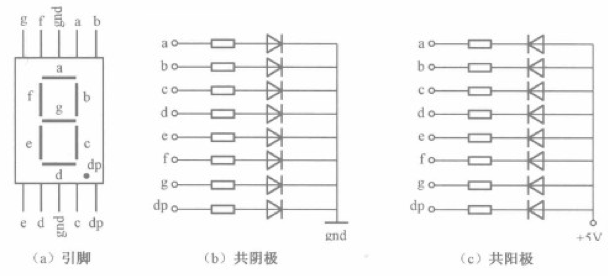

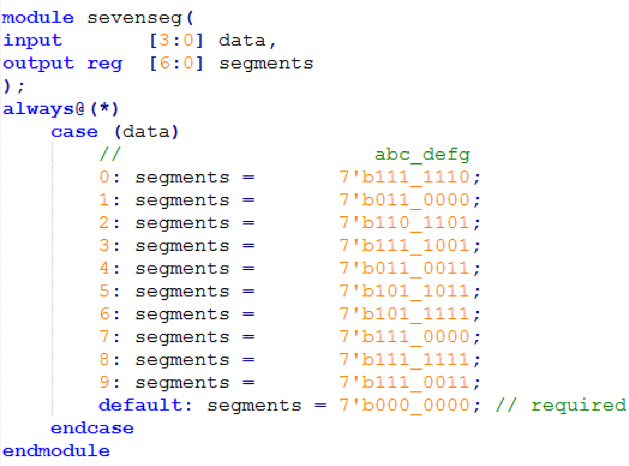

我们最常用的是七段式和八段式LED数码管,八段比七段多了一个小数点,其他的基本相同。所谓的八段就是指数码管里有八个小LED发光二极管,通过控制不同的LED的亮灭来显示出不同的字形。数码管又分为共阴极和共阳极两种类型,其实共阴极就是将八个LED的阴极连在一起,让其接地,这样给任何一个LED的另一端高电平,它便能点亮。而共阳极就是将八个LED的阳极连在一起。其原理如下图  verilog代码  语法说明: case :case语句的各个条件之间没有优先级,且各条件应是互斥的。在组合逻辑电路中使用case语句最后应加上default语句,以防综合出锁存器电路

|